# **CHAPTER 5. CIRCUIT DESCRIPTION**

## [1] Circuit description

## 1. General description

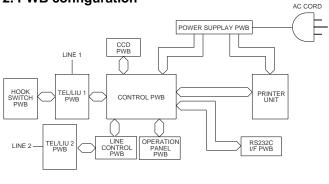

In this machine, the facsimile control block except the printer control is mainly composed of the units shown in Fig. 1.

## 2. PWB configuration

## 1) Control PWB

The control PWB controls all the other operations except the printing operation of the printer and the 2nd line control.

## 2) Line control PWB

The line control PWB controls TX/RX of 2nd line.

## 3) TEL/LIU 1, 2 PWB

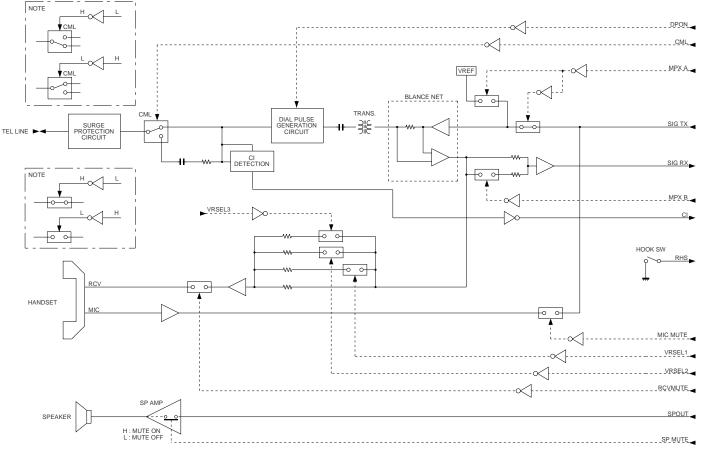

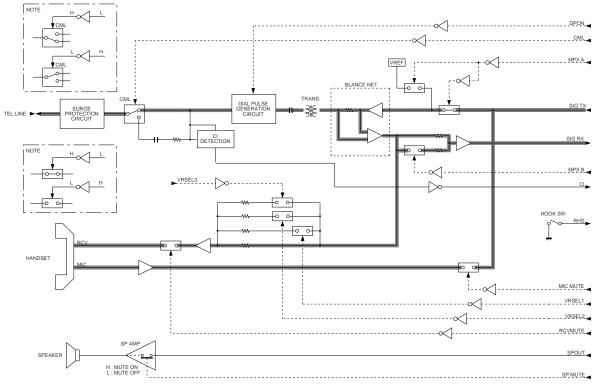

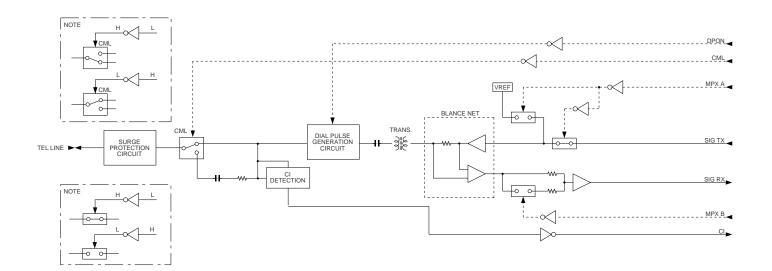

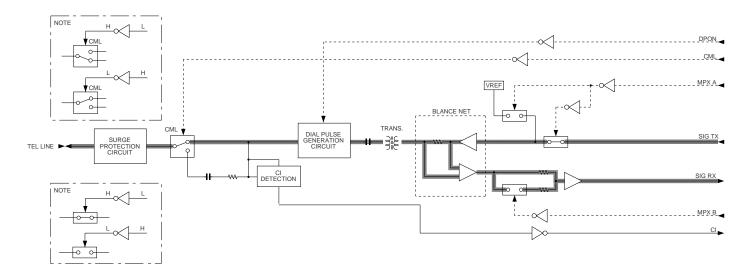

The TEL/LIU PWB controls the I/F telephone function of the circuit with the control signals from the control PWB or the line control PWB.

## 4) CCD PWB

CCD PWB converts the image of the sending or copying draft into the photoelectric signals and transmits the signals to the control PWB.

## 5) Operation panel PWB

The operation panel PWB detects the key input, turns on and off LED and displays LCD according to the control signals from the control PWB.

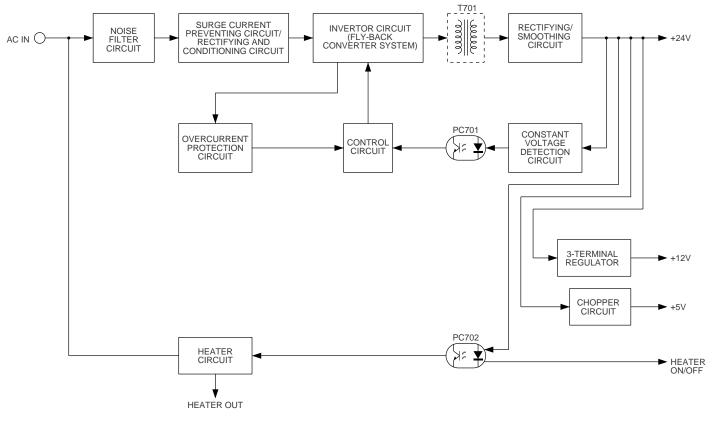

## 6) Power supply PWB

DC voltages (+5V, +12V, +24V) are produced from AC120V, and are supplied to the printer unit and control PWB unit.

## 7) RS232C I/F PWB

The voltage level of the interface signals to PC is converted.

## [2] Circuit description of control PWB

## 1. General description

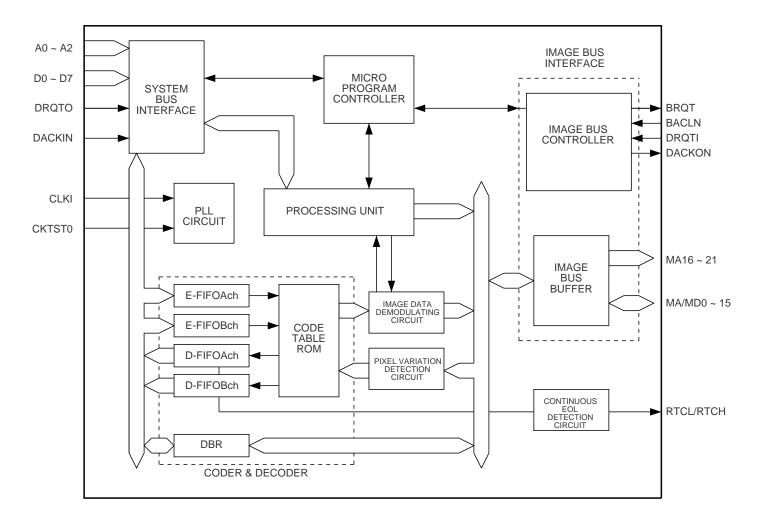

The control PWB is composed of the following blocks.

- 1 Main control block

- 2 EPROM, DRAM, RTC block

- ③ Image memory block

- ④ Modem-1 block

- (5) Reading process and mechanical control block

- 6 Gate array (A) block

- ⑦ Gate array (B) block

- ⑧ CODEC block

- 9 Page memory block

- ① Driver block

- ① Connector block (CNSB)

- Access control block

- ③ Sub-1 CPU block

- ③ Sub-1 ROM, DRAM block

- ① Dual port RAM-1 block

- ⑥ Connector block (CNLIU)

- ③ Sub-1 access control block

## 2. Description of each block

## (1) Main control block

The main control block uses RISC microprocessor HD6437021 as CPU, being composed of ROM (1 MByte) and DRAM (512 KByte).

#### 1) HD6437021 (IC13): pin-100, QFP (main CPU)

The device is a microprocessor which integrates the peripheral functions, using CPU of 32-bit RISC type as the core. In the instrument, the following peripheral functions are mainly used.

- ① ROM of 32 KByte and RAM of 1 KByte are integrated. A part of programs are stored in the integrated ROM.

- ② DMA controller (4 channels are provided, and 2 channels alone are used.)

- ch.0: Used to transmit image data between CODEC (HM514260) and DRAM(IC7).

- ch.3: Used to transmit image data between CPU and DRAM(IC7).

- ③ Clock-synchronous type serial communication interface Commands and statuses are communicated with PCU.

- ④ Start-stop synchronous type serial communication interface Used for PC interface of RS232C system.

- ⑤ Interruption

- IRQ2: Interruption request from gate array (A) (LZ9FJ37A)

- IRQ3: Interruption request from gate array (B) (LR38292)

- IRQ4: Interruption request from CODEC (HD813201F)

- IRQ6: Interruption request from dual port RAM of sub-2 (IDT7130/ IDT7140)

- IRQ7: Interruption request from dual port RAM of sub-1 (IDT7130/ IDT7140)

- IRQ0, IRQ1, IRQ5: Not used.

- NMI : Not used.

- 6 DRAM controller

Addressing to DRAM(IC7) of the system and control and refresh control of  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  signals are executed.

- ⑦ Timer and watch dog timer

- ⑧ General-purpose I/O port Control of analog process of read signals are executed.

- ③ Clock oscillation Ceramic oscillator of 19.66 MHz is connected for operation of 19.66 MHz.

## (2) EPROM, DRAM, RTC block

#### 1) 27C040 (IC5, 11): pin-32, DIP (ROM)

Programs are stored in two 4 Mbit ROM.

#### 2) HM514260 (IC7): pin-40, SOJ (DRAM)

Used as the system memory of main CPU and transmission buffer of communication.

#### 3) NJU6355E (IC127): pin-8, SOP (Real time clock IC)

It is oscillated with the quartz oscillator of 32.768 kHz, and the clock and calendar functions are provided. Even if the power supply of the main body is turned off, it is backed up with lithium battery. This device executes the clock-synchronous type serial communication with the gate array (A), and CPU can know the time and date through the gate array (A).

## HD6437021 (IC13) Terminal descriptions

| Classification            | Code          | Terminal No.<br>(TFP-100B)               | I/O | Name                                             | Function                                                                                                                                                                                                                                                  |

|---------------------------|---------------|------------------------------------------|-----|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power                     | Vcc           | 13, 38, 63,<br>73, 80, 88                | Ι   | Power                                            | Connect to the power supply.<br>Connect Vcc terminals to the power units of all systems.<br>If any open terminal is present, it will not operate                                                                                                          |

|                           | Vss           | 4,15,24,32,<br>41,50,59,70,<br>81,82, 92 | Ι   | Ground                                           | Connect to the ground.<br>Connect Vcc terminals to the power units of all systems.<br>If any open terminal is present, it will not operate.                                                                                                               |

| Clock                     | EXTAL         | 71                                       | I   | External clock                                   | Connect to the quartz oscillator. Moreover, EXTAL terminal can input the external clock.<br>Use the same frequency for the quartz oscillator, external clock and system clock.                                                                            |

|                           | XTAL          | 72                                       | I   | Crystal                                          | Connect the quartz oscillator. Connect the same frequency of the system clock (CK).<br>To input external clock from EXTAL terminal, open EXTAL terminal.                                                                                                  |

|                           | СК            | 69                                       | 0   | System clock                                     | Supply system clock to the peripheral device.                                                                                                                                                                                                             |

| System control            | RES           | 76                                       | Ι   | Reset                                            | If this terminal is turned to the low level when NMI is at the high<br>level, it will be brought into the power-on state. If this terminal is<br>turned to the low level when NMI is at the low level, it will be<br>brought into the manual.reset state. |

|                           | WDTOVF        | 75                                       | 0   | Watch dog timer overflow                         | It is overflow output signal from WDT.                                                                                                                                                                                                                    |

|                           | BREQ          | 60                                       | I   | Bus right request                                | Select the low level to make the external device request the release of bus right.                                                                                                                                                                        |

|                           | BACK          | 58                                       | 0   | Bus right request acknowledge                    | It indicates that the bus right is released to the external device.<br>When receiving BACK signal, the device which outputs BREQ signal can know that bus right is obtained.                                                                              |

| Operation<br>mode control | MD2~<br>MD0   | 79~77                                    | I   | Mode setting                                     | The terminal determines the operation mode.<br>During operation, don't vary any input value. The relationship<br>between MD2 thru MD0 and operation modes are shown in the<br>following list.                                                             |

| Interrupt                 | NMI           | 74                                       | Ι   | No-maskable interrupt                            | This is the interrupt request terminal which can not be masked.<br>Either leading edge or trailing edge is selected for receiving.                                                                                                                        |

|                           | IRQ0~<br>IRQ7 | 65,66,67,68,<br>97,98,99,100             | Ι   | Interrupt request 0<br>thru 7                    | This is the interrupt request terminal which can be masked.<br>Either level input or edge input can be selected.                                                                                                                                          |

|                           | IRQOUT        | 61                                       | 0   | Interrupt request<br>output in the slave<br>mode | It indicates that a factor of interrupt occurs.<br>It indicates that interrupt occurs in the bus release mode.                                                                                                                                            |

| Address                   | A21~A0        | 45~42,40,39,<br>37~33,31~25,<br>23~20    | 0   | Address                                          | Address is output.                                                                                                                                                                                                                                        |

| Data bus                  | AD15~<br>AD0  | 19~16,14,<br>12~5,3~1                    | I/O | Data bus                                         | Bidirectional data bus of 16 bits<br>Multiplex is possible with the low-order 16 bits of the address.                                                                                                                                                     |

|                           | DPH           | 64                                       | I/O | High-order side data bus parity                  | Parity data corresponds to D15 thru D8.                                                                                                                                                                                                                   |

|                           | DPL           | 62                                       | I/O | Low-order side data bus parity                   | Parity data corresponds to D7 thru D0.                                                                                                                                                                                                                    |

### Relationship between MD2 thru MD0 and operation modes

| MD2 | MD1 | MD0 | Operation mode     | IntegratedROM | Bus width of area 0 |

|-----|-----|-----|--------------------|---------------|---------------------|

| 0   | 0   | 0   | Invalid 8-bit size |               | 8-bit size          |

| 0   | 0   | 1   | MCU mode           | invalid       | 16-bit size         |

| 0   | 1   | 0   |                    | Valid         | —                   |

| 0   | 1   | 1   | (Reserved)         | —             | —                   |

| 1   | 0   | 0   | (Reserved)         | —             | —                   |

| 1   | 0   | 1   | (Reserved)         | —             | —                   |

| 1   | 1   | 0   | (Reserved)         | —             | —                   |

| 1   | 1   | 1   | (Reserved)         | —             | —                   |

(Continuing)

## HD6437021 (IC13) Terminal descriptions

| Classification                           | Code              | Terminal No.<br>(TFP-100B) | I/O | Name                                                    | Function                                                                                                |

|------------------------------------------|-------------------|----------------------------|-----|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Bus control                              | WAIT              | 54                         | I   | Wait                                                    | It is input to insert Tw into the bus cycle during access to the external space.                        |

|                                          | RAS               | 52                         | 0   | Low address strobe                                      | Timing signal of low address strobe of DRAM                                                             |

|                                          | CASH              | 47                         | 0   | High-order column<br>address strobe                     | Timing signal of column address strobe of DRAM<br>It is output for access to high-order 8 bits of data. |

|                                          | CASL              | 49                         | 0   | Low-order column<br>address strobe                      | Timing signal of column address strobe of DRAM<br>It is output for access to low-order 8 bits of data.  |

|                                          | RD                | 57                         | 0   | Read                                                    | It indicates that outside is read out.                                                                  |

|                                          | WRH               | 56                         | 0   | High-order write                                        | It indicates writing at the external high-order 8 bits.                                                 |

|                                          | WRL               | 55                         | 0   | Low-order write                                         | It indicates writing at the external low-order 8 bits.                                                  |

|                                          | CS0~CS7           | 46~49,<br>51~54            | 0   | Chip select 0 thru 7                                    | Chip select signal for external memory or device                                                        |

|                                          | ĀĦ                | 61                         | 0   | Address hold                                            | Address hold timing signal for device which uses multiplex bus of address/data                          |

|                                          | HBS,<br>LBS       | 20<br>56                   | 0   | Low-/high-order byte strobe                             | Strobe signal of high/low byte<br>(Commonly used with AO, WRH.)                                         |

|                                          | WR                | 55                         | 0   | Write                                                   | Output during writing. (Commonly used with WRL.)                                                        |

| DMAC                                     | DREQ0,<br>DREQ1   | 66,68                      | I   | DMA transfer request (Channels 0 and 1)                 | Input terminal of DMA transfer request from external                                                    |

|                                          | DACK0,<br>DACK1   | 65,67                      | 0   | DMA transfer request<br>receiving (Channels<br>0 and 1) | It indicates that DMA transfer request is received.                                                     |

| 16-bit<br>integrated<br>timer pulse unit | TIOCA0,<br>TIOCB0 | 51,<br>53                  | I/O | ITU input<br>capture/output<br>conveyor (Channel 0)     | Output terminal of input capture input/output conveyor                                                  |

| (ITU)                                    | TIOCA1,<br>TIOCB1 | 62,<br>64                  | I/O | ITU input<br>capture/output<br>conveyor (Channel 1)     | Output terminal of input capture input/output conveyor                                                  |

|                                          | TIOCA2,<br>TIOCB2 | 83,<br>84                  | I/O | ITU input<br>capture/output<br>conveyor (Channel 2)     | Output terminal of input capture input/output conveyor                                                  |

|                                          | TIOCA3,<br>TIOCB3 | 85,<br>86                  | I/O | ITU input<br>capture/output<br>conveyor (Channel 3)     | Output terminal of input capture input/output conveyor                                                  |

|                                          | TIOCA4,<br>TIOCB4 | 87,<br>89                  | I/O | ITU input<br>capture/output<br>conveyor (Channel 4)     | Output terminal of input capture input/output conveyor                                                  |

|                                          | TOCXA4,<br>TOCXB4 | 90,<br>91                  | 0   | ITU output conveyor<br>(Channel 4)                      | Output terminal of output conveyor                                                                      |

|                                          | TCLKA~<br>TCLKD   | 65,66,90,<br>91            | I   | ITU timer clock input                                   | External clock input terminal to counter of ITU                                                         |

| Timing pattern controller (TPC)          | TP15~<br>TP0      | 100~93,<br>91~89,<br>87~83 | 0   | Timing pattern<br>Output 15 thru 0                      | Output terminal of timing pattern                                                                       |

| Serial communication                     | TxD0,<br>TxD1     | 94,<br>96                  | 0   | Sending data<br>(Channels 0 and 1                       | Sending data output terminal of SCI0, 1                                                                 |

| nterface (SCI)                           | RxD0,<br>RxD1     | 93,<br>95                  | I   | Receiving data<br>(Channels 0 and 1)                    | Receiving data input terminal of SCI0, 1                                                                |

|                                          | SCK0,<br>SCK1     | 97,<br>98                  | I/O | Serial clock<br>(Channels 0 and 1)                      | Clock input/output terminal of SCI0, 1                                                                  |

| I/O port                                 | PA15~<br>PA0      | 68~64,<br>62~60,<br>58~51  | I/O | Port A                                                  | Input/output terminal of 16 bits<br>Input/output can be assigned for each bit.                          |

|                                          | PB15~<br>PB0      | 100~93,<br>91~89,<br>87~83 | I/O | Port B                                                  | Input/output terminal of 16 bits<br>Input/output can be assigned for each bit.                          |

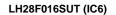

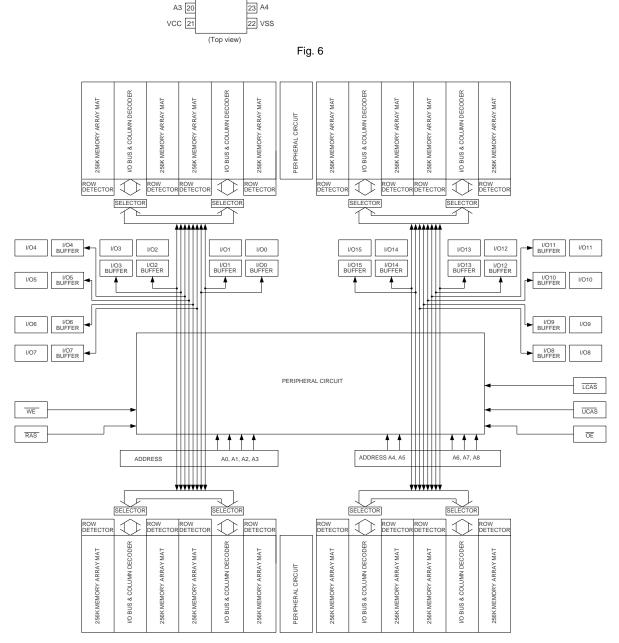

## (3) Image memory block

This block is composed of 2 MByte flash memory and 128 KByte SRAM. Moreover, a maximum of 16 MByte (when FO-16MG is installed) of image memory can be extended by install-ing the option memory of the connector CNOP.

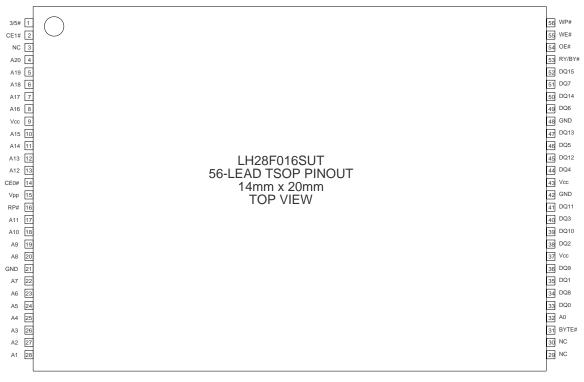

## 1) LH28F016SUT (IC6) — Pin-56, TSOP (16 Mbit flash memory)

The memory is a non-volatile type whose content does not erase even if power is turned off, and stores the copied, sent and received image data. Moreover, the initially registered data, registered content of "RE-LAY" key and registered content of "CONF" key are stored.

## 2) KM68512ALG-5L(IC2, IC9) — pin-32, SOP (512 Kbit SRAM)

The setting of receiving mode, optional setting content, soft switch content and dairy data are stored. Even if the power supply of the main body is turned off, it is backed up with a lithium battery. The above functions are controlled by getting an access to the inter-face memory in the modem through the data bus from sub-1 CPU (IC4) of the control PWB. The interface memory is composed of 32 8-bit registers, and is controlled with the bank switch. Accordingly, the register is selected by the register selection signals (RS4 to RS0) of 5 bits and chip selection signal (CS). The major content controlled by these reg-isters is as follows.

#### 1) Configuration register

Mode setting of V34, V17, V29, V27, G2, FSK and tone transmission

#### 2) Option register

Equalizing method of equalizer, carrier detection threshold, addition of echo suppressor protect tone, and setting of transmission/reception mode

#### 3) Others

G2AGC control, tone frequency setting, and so on

Moreover, data is read from these registers through the data bus to monitor the statuses of the modem such as tone detection, training pattern detection and so on.

Next, transmission/reception operation is described.

During sending, the sent data is given from the control block to the modem through the data bus. Then, it is modulated and sent to TEL/LIU 1 PWB with SIGTX signal. During receiving, the received data is sent from TEL/LIU 1 PWB to the modem with SIGRX signal and is demodulated. Then, it is sent to the control block with the data bus. The above operation is done with the modem LSI (IC).

### (4) Modem-1 block

The block is mainly composed of the modem R288F (IC3), and is provided with the following modem function.

| Configuration   | Modulation 1 | Carrier Frequency<br>(Hz) ± 0.01 % | Data Rate (bps)<br>± 0.01 % | Symbol Rate (Symbols/Sec.) | Bits/Symbol-<br>Data | Bits/Symbol-<br>TCM | Constellation<br>Points |

|-----------------|--------------|------------------------------------|-----------------------------|----------------------------|----------------------|---------------------|-------------------------|

| V. 34 33600 TCM | ТСМ          | Note 2                             | 33600                       | 3429 only                  | Note 2               | Note 2              | Note 2                  |

| V. 34 31200 TCM | TCM          | Note 2                             | 31200                       | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 28800 TCM | TCM          | Note 2                             | 28800                       | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 26400 TCM | TCM          | Note 2                             | 26400                       | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 24000 TCM | TCM          | Note 2                             | 24000                       | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 21600 TCM | TCM          | Note 2                             | 21600                       | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 19200 TCM | TCM          | Note 2                             | 19200                       | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 16800 TCM | TCM          | Note 2                             | 16800                       | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 14400 TCM | TCM          | Note 2                             | 14400                       | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 12000 TCM | TCM          | Note 2                             | 12000                       | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 9600 TCM  | TCM          | Note 2                             | 9600                        | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 7200 TCM  | TCM          | Note 2                             | 7200                        | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 4800 TCM  | TCM          | Note 2                             | 4800                        | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 34 2400 TCM  | TCM          | Note 2                             | 2400                        | Note 2                     | Note 2               | Note 2              | Note 2                  |

| V. 23 1200/75   | FSK          | 1700/420                           | 1200/75                     | 1200                       | 1                    | 0                   | —                       |

| V. 21           | FSK          | 1080/1750                          | 0-300                       | 300                        | 1                    | 0                   | —                       |

| V. 17 14400 TCM | ТСМ          | 1800                               | 14400                       | 2400                       | 6                    | 1                   | 128                     |

| V. 17 12000 TCM | ТСМ          | 1800                               | 12000                       | 2400                       | 5                    | 1                   | 64                      |

| V. 17 9600 TCM  | ТСМ          | 1800                               | 9600                        | 2400                       | 4                    | 1                   | 32                      |

| V. 17 7200 TCM  | TCM          | 1800                               | 7200                        | 2400                       | 3                    | 1                   | 16                      |

| V. 29 9600      | QAM          | 1700                               | 9600                        | 2400                       | 4                    | 0                   | 16                      |

| V. 29 7200      | QAM          | 1700                               | 7200                        | 2400                       | 3                    | 0                   | 8                       |

| V. 29 4800      | QAM          | 1700                               | 4800                        | 2400                       | 2                    | 0                   | 4                       |

| V. 27 4800      | DPSK         | 1800                               | 4800                        | 1600                       | 3                    | 0                   | 8                       |

| V. 27 2400      | DPSK         | 1800                               | 2400                        | 1200                       | 2                    | 0                   | 4                       |

| V. 21 Channel 2 | FSK          | 1750                               | 300                         | 300                        | 1                    | 0                   | _                       |

Notes:

| 1. Modulation legend: TCM:     | Trellis-Coded Modulation |

|--------------------------------|--------------------------|

| FSK:                           | Frequency Shift Keying   |

| 2. Adaptive: established durir | ng handshake:            |

QAM: Quadrature Amplitude Modulation DPSK: Differential Phase Shift Keying

| nive, established during har | iusiiake.         |                    |

|------------------------------|-------------------|--------------------|

|                              | Carrier Fre       | equency (Hz)       |

| Symbol Rate (Baud)           | V. 34 Low Carrier | V. 34 High Carrier |

| 2400                         | 1600              | 1800               |

| 2800                         | 1680              | 1867               |

| 3000                         | 1800              | 2000               |

| 3200                         | 1829              | 1920               |

| 3429                         | 1959              | 1959               |

## (5) Reading process and mechanical control block

#### 1) Reading process block

The reading block is composed of the following blocks.

- 1 CCD drive block (IC14: LZ9FJ37A)

- 2 Analog process block

- Analog LSI(IC25: TLS1049)

- Tr.C/R etc

- ③ Binary coding block/read data control block (IC14:LZ9FJ37A)

The details of each block are described as follows.

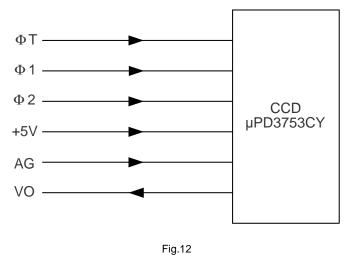

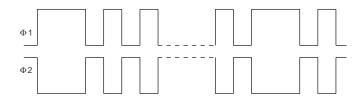

#### a) CCD drive block

The clock signal necessary for CCD drive is supplied from gate array (A) to CCD.

Hereafter, the clocks are outlined.

- $\bullet \ \varphi 1/\varphi 2$  --- Transmission clock

#### b) Analog process block

The analog video signal supplied from CCD PWB is directly supplied to the analog LSI.

On the other hand, as the reference level (reference voltage) of A/D conversion, the peak voltage of the video signal detected in the peak hold circuit is supplied to the A/D conversion block in the stan-dard/ fine/ super fine mode and the fixed voltage is supplied to the block in the half tone mode. After the offset part is cut in the analog LSI, 7-bit digital video signal is supplied to the gate array by using the integrated 7-bit high speed A/D converter according to the A/D conversion clock output from the gate array.

#### c) Binary coding block/read data control block

It is composed of the processing circuit (IC14: LZ9FJ37A) which integrates various binary coding algorithms and the reading line memo-ries (IC23, IC24: LH5268TH10) which record necessary data. The digital video signal input in 7 bits is judged as 2 values (black(1) and white (0), and the data is transmitted to the gate array (B) (IC18: LR38292) in the serial mode and is stored in the page memory. The contents binary-coded here are as follows.

- Shading compensation

- Half tone process (error diffusion process)

- MTF compensation

#### 2) Mechanical control block

The mechanical control block is mainly composed of the gate array (A) (IC14: LZ9FJ37A) to control the following.

#### (a) Sending motor control

The revolution speed and timing of the sending motor are controlled to output the control signals to the motor driver (IC20, IC21).

#### (b) End stamp and LED lamp control

On/off of the end stamp and LED lamp is controlled with the software.

### (6) Gate array (A) block

This block is mainly composed of the gate array (A) (IC14: LZ9FJ37A), and has the following functions.

- 1 Mapper

- Mapping is executed in the memory area of the memories, gate array (B), modem and CODEC.

- 2 Reading process

- Refer to 1) Reading process block of 2-4 Reading and mechanical control block.

- 3 Mechanical control block

Refer to 2) Mechanical control block of 2-5 Reading and mechani-cal control block.

4 IC interface for clock

Writing and reading to IC (IC127: NJU6355E) for clock is executed in the clock-synchronous type serial transfer mode.

- ⑤ PC interface

- I/O port control (communication is done with main CPU.)

- Detection of communication speed with AT command monitor

- ⑥ Generation of alarm sound and ringer sound The keys on the operation panel are pressed to respectively generate the key input sound, alarm sound and ringer sound.

## LZ9FJ37A (IC14) Terminal descriptions

| PIN      | I/O | Name    | Function                                  | PIN      | I/O | Name   | Function                             |

|----------|-----|---------|-------------------------------------------|----------|-----|--------|--------------------------------------|

| 1        | 0   | DP      | Dial pulse control                        | 52       | I/O | D14    | System data input/output             |

| 2        | 0   | DT4     | Output port                               | 53       | I/O | D13    | System data input/output             |

| 3        | 0   | DT3     | Output port                               | 54       | I/O | D12    | System data input/output             |

| 4        | 0   | DT2     | Output port                               | 55       | I   | XCS6   | Chip select 6 signal input           |

| 5        | 0   | DT1     | Output port                               | 56       | I   | XCS2   | Chip select 2 signal input           |

| 6        | 0   | BZ      | Buzzer output                             | 57       | I/O | D11    | System data input/output             |

| 7        | 0   | BZSL    | Output port                               | 58       | I/O | D10    | System data input/output             |

| 8        | I   | SDT     | Input port                                | 59       | I/O | D9     | System data input/output             |

| 9        | I   | XRHS    | Input port                                | 60       | I/O | D8     | System data input/output             |

| 10       | I   | XCI     | Input port                                | 61       | _   | GND    | Ground                               |

| 11       | I   | XHS1    | Input port                                | 62       | _   | VDD    | Power supply                         |

| 12       | I   | XHS2    | Input port                                | 63       | I/O | D7     | System data input/output             |

| 13       | I   | XEXHS1  | Input port                                | 64       | I/O | D6     | System data input/output             |

| 14       | I   | XEXHS2  | Input port                                | 65       | I/O | D5     | System data input/output             |

| 15       | 0   | CRNT    | Output port                               | 66       | I/O | D4     | System data input/output             |

| 16       | 0   | TXB1    | B-phase current control output 1          | 67       | 1   | A19    | System address input/output          |

| 17       | 0   | ТХВО    | B-phase current control output 0          | 68       | 1   | A20    | System address input/output          |

| 18       | 0   | TXA1    | A-phase current control output 1          | 69       | 1   | A21    | System address input/output          |

| 19       | 0   | TXA0    | A-phase current control output 0          | 70       | I/O | D3     | System data input/output             |

| 20       | _   | VDD     | Power supply                              | 71       | I/O | D2     | System data input/output             |

| 21       |     | GND     | Ground                                    | 72       | I/O | D1     | System data input/output             |

| 22       | 0   | ТХРВ    | B-phase current direction setting         | 73       | I/O | D0     | System data input/output             |

| 23       | 0   | ТХРА    | A-current direction setting               | 74       | 1   | A6     | System address input/output          |

| 24       | 0   | LEDON   | LED light source control                  | 75       | 1   | A5     | System address input/output          |

| 25       | 0   | PLG10N  | Plunger 1 control                         | 76       |     | A4     | System address input/output          |

| 26       | 0   | PLG0ON  | Plunger 0 control                         | 77       |     | A3     | System address input/output          |

| 27       | _   | GND     | Ground                                    | 78       | 1   | A2     | System address input/output          |

| 28       | 1   | CLKR    | Sending system control basic clock input  | 79       | 1   | A1     | System address input/output          |

| 29       |     | XFLBSY  | Flash memory busy signal input            | 80       |     | GND    | Ground                               |

| 30       | 0   | FLBK1   | Bank control 1                            | 81       | 1   | TEST   | Test terminal                        |

| 31       | 0   | FLBK2   | Bank control 2                            | 82       | 0   | XSCCLK | Reading serial clock                 |

| 32       | 0   | FLBK3   | Bank control 3                            | 83       | 0   | XSRVID | Reading serial data                  |

| 33       | 0   | XFLOPT  | Chip select (flash option)                | 84       | 0   | XSTVD  | Reading valid data output gate       |

| 34       | 0   | XFLSTD  | Chip select (flash standard)              | 85       | 1   | TXIN   | Data receiving from SH1              |

| 35       | 0   | XPGMSL  | Chip select (EPROM)                       | 86       | 0   | RXOUT  | Data sending to SH1                  |

| 36       | 0   | XSRAM1  | Chip select (SRAM option)                 | 87       | 0   | TXOUT  | Data sending signal to PC            |

| 37       | 0   | XSRAM0  | Chip select (SRAM standard)               | 88       | 1   | RXIN   | Data receiving signal from PC        |

| 38       | 0   | XINTRQ  | Interrupt request output                  | 89       | 0   | XRTS   | Sending of send-ready signal to PC   |

| 39       | 0   | XREVSL  | Chip select (spare)                       | 90       | 0   | XDSR   | Sending of data terminal ready to PC |

| 40       | 1   | XRESET  | System reset                              | 91       | 1   | XCTS   | Sending request from PC              |

| 41       |     | GND     | Ground                                    | 92       | 1   | XDTR   | Data set ready sending to PC         |

| 42       |     | CLKF    | System clock                              | 93       | 0   | XRSCI  | Call-back to PC                      |

| 43       | 0   | XCDCSL  | Chip select                               | 94       | 0   | XRSCD  | Carrier detection to PC              |

| 43       | 0   | XGACSL1 | Chip select (spare)                       | 94<br>95 | 1   | XRSOPT | PCI/F presence detection             |

| 44       | 0   | XGACSLI | Chip select                               | 95<br>96 | 0   | RTCIO  | RTC input/output control             |

| 45       | 0   | XGAUSLO | Chip select (gate array B)                | 90<br>97 | 0   | RTCCE  | RTC chip select                      |

|          |     | XWR     | System write output                       |          | 0   | RTCCE  | RTC data transfer clock              |

| 47<br>48 | 0   | XRD     | System write output<br>System read signal | 98<br>99 | 1/0 | RTCDT  |                                      |

|          |     |         |                                           |          |     |        | RTC data input/output                |

| 49       |     | XWRH    | System write (high-order byte) signal     | 100      |     | VDD    | Power supply                         |

| 50       |     | XWRL    | System write (low-order byte) signal      | 101      |     | GND    | Ground                               |

| 51       | I/O | D15     | System data input/output                  | 102      | 0   | PHIA   | CCD clock A                          |

## LZ9FJ37A (IC14) Terminal descriptions

| PIN | I/O | Name    | Function                         | PIN | I/O | Name    | Function                      |

|-----|-----|---------|----------------------------------|-----|-----|---------|-------------------------------|

| 103 | 0   | PHIB    | CCD clock B                      | 154 | 0   | RA3     | Reading memory address output |

| 104 | 0   | PHIR    | CCD reset signal                 | 155 | 0   | RA4     | Reading memory address output |

| 105 | 0   | XPHIT   | CCD #T output                    | 156 | 0   | RA5     | Reading memory address output |

| 106 | I   | XA3FRS  | Input port                       | 157 | 0   | RA6     | Reading memory address output |

| 107 | I   | XB4FRS  | Input port                       | 158 | 0   | RA7     | Reading memory address output |

| 108 | I   | XFRSNS  | Input port                       | 159 | 0   | XMDMRST | Modem reset output            |

| 109 | I   | XORGSNS | Input port                       | 160 | _   | GND     | Ground                        |

| 110 | I   | XDRSNS  | Input port                       |     |     |         |                               |

| 111 | 0   | XPHISH  | Video sample hold                |     |     |         |                               |

| 112 | 0   | XPHIBL  | Line clamp                       |     |     |         |                               |

| 113 | 0   | HTEN    | Half tone select output          |     |     |         |                               |

| 114 | 0   | XGTW    | Peak hold gate                   |     |     |         |                               |

| 115 | 0   | XPGST   | Peak hold circuit clear          |     |     |         |                               |

| 116 | 0   | ADCK    | ADC sampling clock output        |     |     |         |                               |

| 117 | I   | B7      | Video data input                 |     |     |         |                               |

| 118 | I   | B6      | Video data input                 |     |     |         |                               |

| 119 | I   | B5      | Video data input                 |     |     |         |                               |

| 120 | I   | B4      | Video data input                 |     |     |         |                               |

| 121 | _   | GND     | Ground                           |     |     |         |                               |

| 122 | I   | B3      | Video data input                 |     |     |         |                               |

| 123 | I   | B2      | Video data input                 |     |     |         |                               |

| 124 | I   | B1      | Video data input                 |     |     |         |                               |

| 125 | I   | B0      | Video data input                 |     |     |         |                               |

| 126 | 0   | RA12    | Reading memory address output    |     |     |         |                               |

| 127 | 0   | RA11    | Reading memory address output    |     |     |         |                               |

| 128 | 0   | RA10    | Reading memory address output    |     |     |         |                               |

| 129 | 0   | RA9     | Reading memory address output    |     |     |         |                               |

| 130 | 0   | RA8     | Reading memory address output    |     |     |         |                               |

| 131 | 0   | XRWE    | Reading memory write output      |     |     |         |                               |

| 132 | 0   | XROE    | Reading memory read output       |     |     |         |                               |

| 133 | I/O | RAD15   | Reading memory data input/output |     |     |         |                               |

| 134 | I/O | RAD14   | Reading memory data input/output |     |     |         |                               |

| 135 | I/O | RAD13   | Reading memory data input/output |     |     |         |                               |

| 136 | I/O | RAD12   | Reading memory data input/output |     |     |         |                               |

| 137 | I/O | RAD11   | Reading memory data input/output |     |     |         |                               |

| 138 | I/O | RAD10   | Reading memory data input/output |     |     |         |                               |

| 139 | I/O | RAD9    | Reading memory data input/output |     |     |         |                               |

| 140 | I/O | RAD8    | Reading memory data input/output |     |     |         |                               |

| 141 | —   | GND     | Ground                           |     |     |         |                               |

| 142 | —   | VDD     | Power supply                     |     |     |         |                               |

| 143 | I/O | RAD7    | Reading memory data input/output |     |     |         |                               |

| 144 | I/O | RAD6    | Reading memory data input/output |     |     |         |                               |

| 145 | I/O | RAD5    | Reading memory data input/output |     |     |         |                               |

| 146 | I/O | RAD4    | Reading memory data input/output |     |     |         |                               |

| 147 | I/O | RAD3    | Reading memory data input/output |     |     |         |                               |

| 148 | I/O | RAD2    | Reading memory data input/output |     |     |         |                               |

| 149 | I/O | RAD1    | Reading memory data input/output |     |     |         |                               |

| 150 | I/O | RAD0    | Reading memory data input/output |     |     |         |                               |

| 151 | 0   | RA0     | Reading memory address output    |     |     |         |                               |

| 152 | 0   | RA1     | Reading memory address output    |     |     |         |                               |

| 153 | 0   | RA2     | Reading memory address output    |     |     |         |                               |

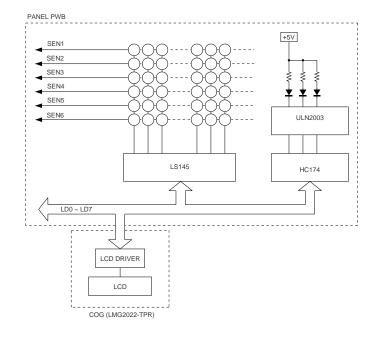

## (7) Gate array (B) block

The block is composed of the gate array (B) and SRAM (2 KByte).

## 1) LR38292(IC18) -- pin-160, QFP (gate array B)

The device has the following functions.

① Printing data process

The image data of the page memory for printing is converted into 400 dpi, and the smoothing and contracting processes are applied.

2 Printer (PCU) interface

The control of resetting and so on to PCU and the image data processed in Item ① above are synchronized with the signal (HSYNC) from PCU and are transmitted to PCU in the serial mode.

- ③ DMA controller

- (a) The binary-coded data of the draft transmitted in the serial mode from the gate array (A) LZ9FJ37A(IC14) and read with the scanner are transmitted to the page memory.

- (b) The image data which will be printed are read from the page memory, and the process ① is applied to transmit the data to PCU in the serial mode.

- ④ CODEC (HD813201F) interface

- (a) The timing is controlled for CPU to get an access to CODEC.

- (b) The timing is controlled for CODEC to get an access to the page memory.

- **⑤ DRAM controller**

- Since DRAM is used for the page memory, and the address, RAS and CAS are controlled and refresh-controlled.

- 6 Panel interface

The key input detection on the operation panel, LED lighting con-trol and LCD display control are executed.

## 2) LH5116NA-10 (IC22) -- pin-24, SOP (16-bit SRAM)

This SRAM is a line memory for the printing data process (resolution power conversion, smoothening and contracting to 404 dpi) of the gate array (B).

### LR38292 (IC18) Terminal descriptions

| LING0292 ( | IC18) Term | iinai u | escriptions                              |

|------------|------------|---------|------------------------------------------|

| Pin        | Name       | I/O     | Function                                 |

| 20         | VCC        |         | Power supply                             |

| 62         | VCC        |         |                                          |

| 100        | VCC        |         |                                          |

|            |            |         |                                          |

| 142        | VCC        |         |                                          |

| 16         | GND        |         | Ground                                   |

| 21         | GND        |         |                                          |

| 35         | GND        |         |                                          |

| 48         | GND        |         |                                          |

| 61         | GND        |         |                                          |

|            |            |         |                                          |

| 78         | GND        |         |                                          |

| 87         | GND        |         |                                          |

| 101        | GND        |         |                                          |

| 125        | GND        |         |                                          |

| 134        | GND        |         |                                          |

| 143        | GND        |         |                                          |

|            |            | 0       | Manual report signal                     |

| 65         | MANRESB    | 0       | Manual reset signal                      |

| 66         | RESETB     |         | Reset signal                             |

| 89         | A5         | 1       | Address signal on the system side        |

| 90         | A4         |         |                                          |

| 91         | A3         |         |                                          |

| 92         | A2         |         |                                          |

|            |            |         |                                          |

| 93         | A1         | 1/2     | Data has also to the first               |

| 70         | D15        | I/O     | Data bus signal on the system side       |

| 71         | D14        |         |                                          |

| 72         | D13        |         |                                          |

| 73         | D12        |         |                                          |

| 74         | D11        |         |                                          |

|            |            |         |                                          |

| 75         | D10        |         |                                          |

| 76         | D9         |         |                                          |

| 77         | D8         |         |                                          |

| 79         | D7         |         |                                          |

| 80         | D6         |         |                                          |

| 81         | D0         |         |                                          |

|            |            |         |                                          |

| 82         | D4         |         |                                          |

| 83         | D3         |         |                                          |

| 84         | D2         |         |                                          |

| 85         | D1         |         |                                          |

| 86         | D0         |         |                                          |

| 88         | CSB        | 1       | Chip select signal of gate array LR38292 |

|            |            |         |                                          |

| 97         | RDB        |         | Read signal on the system bus side       |

| 98         | WRB        |         | Write signal on the system bus side      |

| 115        | SHCK0B     | 0       | Reversion output of clock (SHCK) from    |

|            |            |         | CPU                                      |

| 116        | SHCK       | 1       | Clock (19.6 MHz) from CPU                |

| 95         | GAINTB     | 0       | Interrupt request signal to CPU of gate  |

| 90         |            | U       |                                          |

|            | 0000       |         | array LR38292                            |

| 94         | CDCINTB    | 0       | Reversion output (to CPU) of interrupt   |

|            |            |         | request signal from HD813201F            |

| 96         | DREQ0B     | 0       | Reversion output (to CPU) of DMA         |

| 1          |            |         | transfer request signal from HD813201F   |

| 99         | RSTCDCB    | 0       | Reset signal to HD813201F (Default:      |

| 33         |            | U       | J N N                                    |

| 100        | 0000       |         | Low)                                     |

| 102        | CDCINT     |         | Interrupt request signal from HD813201F  |

| 103        | BRQT       | I       | Bus right request signal of image bus    |

|            |            |         | from HD813201F                           |

| 104        | BACKB      | 0       | Bus right permission signal of image bus |

| -          |            | -       | to HD813201F                             |

| 105        | DRQ0       |         | DMA transfer request signal from         |

| 103        |            | 1       |                                          |

|            | DAG:       |         | HD813201F                                |

| 106        | DACK0B     | 0       | Acknowledge signal of DMA transfer to    |

|            |            |         | HD813201F                                |

| 107        | CSCDCB     | I       | Chip select signal to HD813201F          |

| 108        | MDENB      | İ       | Data enable signal of image bus from     |

|            |            | •       | HD813201F                                |

| 100        |            |         |                                          |

| 109        | READY      | 0       | Ready signal of image bus access to      |

|            |            |         | HD813201F                                |

| 110        | MAS        | I       | Address strobe signal of image bus of    |

| 1          |            |         | HD813201F                                |

|            |            |         |                                          |

## LR38292 (IC18) Terminal descriptions

| Pin                                                                                                                                          |                                                                                                                          |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 444                                                                                                                                          | Name                                                                                                                     | I/O                                                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 111                                                                                                                                          | MAENB                                                                                                                    |                                                                         | Address enable signal of image bus of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                              |                                                                                                                          |                                                                         | HD813201F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 440                                                                                                                                          | CKACNA                                                                                                                   | 1                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 112                                                                                                                                          | CK16M                                                                                                                    |                                                                         | 16 MHz clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 113                                                                                                                                          | RDCDC                                                                                                                    | 0                                                                       | Register read signal (active H) of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                              |                                                                                                                          |                                                                         | HD813201F of CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 114                                                                                                                                          | RDCDCB                                                                                                                   | 0                                                                       | Register read signal (active L) of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                              |                                                                                                                          | U                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                              |                                                                                                                          |                                                                         | HD813201F of CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 139                                                                                                                                          | MA20                                                                                                                     | 1                                                                       | Address of image bus of HD813201F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 138                                                                                                                                          | MA19                                                                                                                     |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 137                                                                                                                                          | MA18                                                                                                                     |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 136                                                                                                                                          |                                                                                                                          |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                              | MA17                                                                                                                     |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 135                                                                                                                                          | MA16                                                                                                                     |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 133                                                                                                                                          | MAD15                                                                                                                    | I/O                                                                     | Address/data of image bus of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

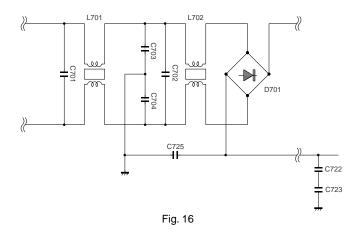

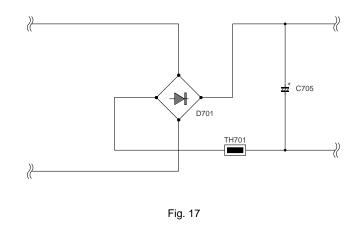

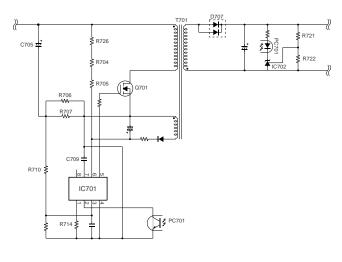

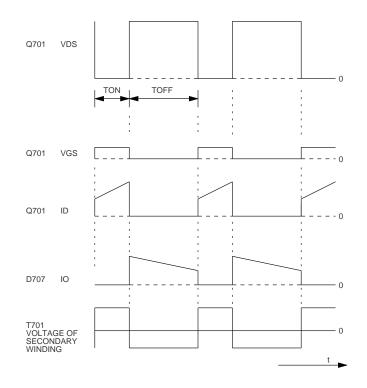

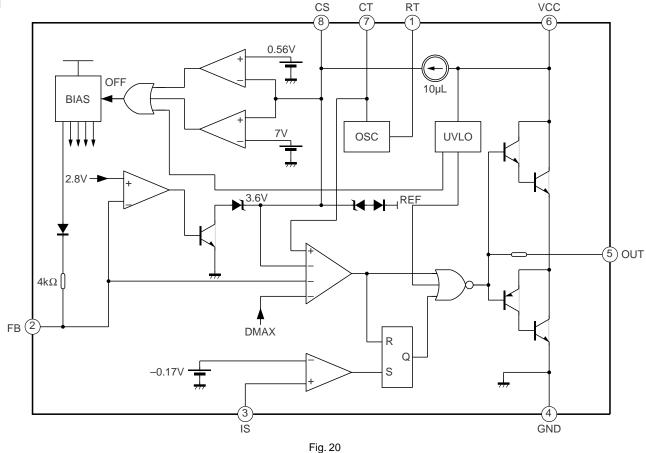

| 132                                                                                                                                          | MAD14                                                                                                                    |                                                                         | HD813201F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |